---

### High-performance Sound Processor with 32 APUs (audio processing unit) and DSP with FPU.

---

#### Features

- Dynamic efficiency power

- 1.7V to 3.6V power supply

- -40°C to 125°C temperature range

- 30nA Standby mode

- 84µA/MHz run mode

- Core: Arm® 32-bit Cortex®-M4 CPU with FPU, DSP

- Audio Processing Unit

- 32x Independent APUs with DMA

- Clock Sources

- 4 to 26 MHz crystal oscillator

- 32 kHz crystal oscillator for RTC

- Memories

- Up to 128KB single bank Flash, proprietary code readout protection

- 32 KB of SRAM

- AES Bootloader

- Communication interfaces

- 2x I2S (audio interface)

- 2x I2C

- 2x UARTs

- DMA controller

#### Description

The AMT3459 device are the dynamic efficiency power and high performance microcontroller with 32 independent APUs. Each can be used as programmable filters for the audio record path.

#### Device Information

| Part Number | Package   | Size, mm |

|-------------|-----------|----------|

| AMT3459     | UFQFPN-48 | 7x7      |

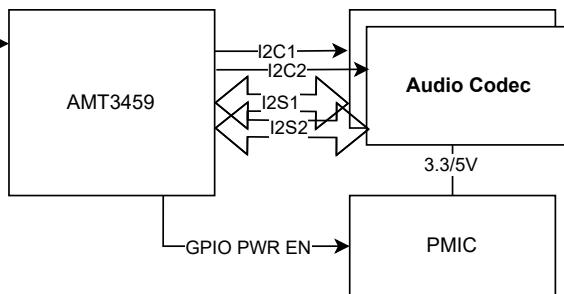

#### Typical Application

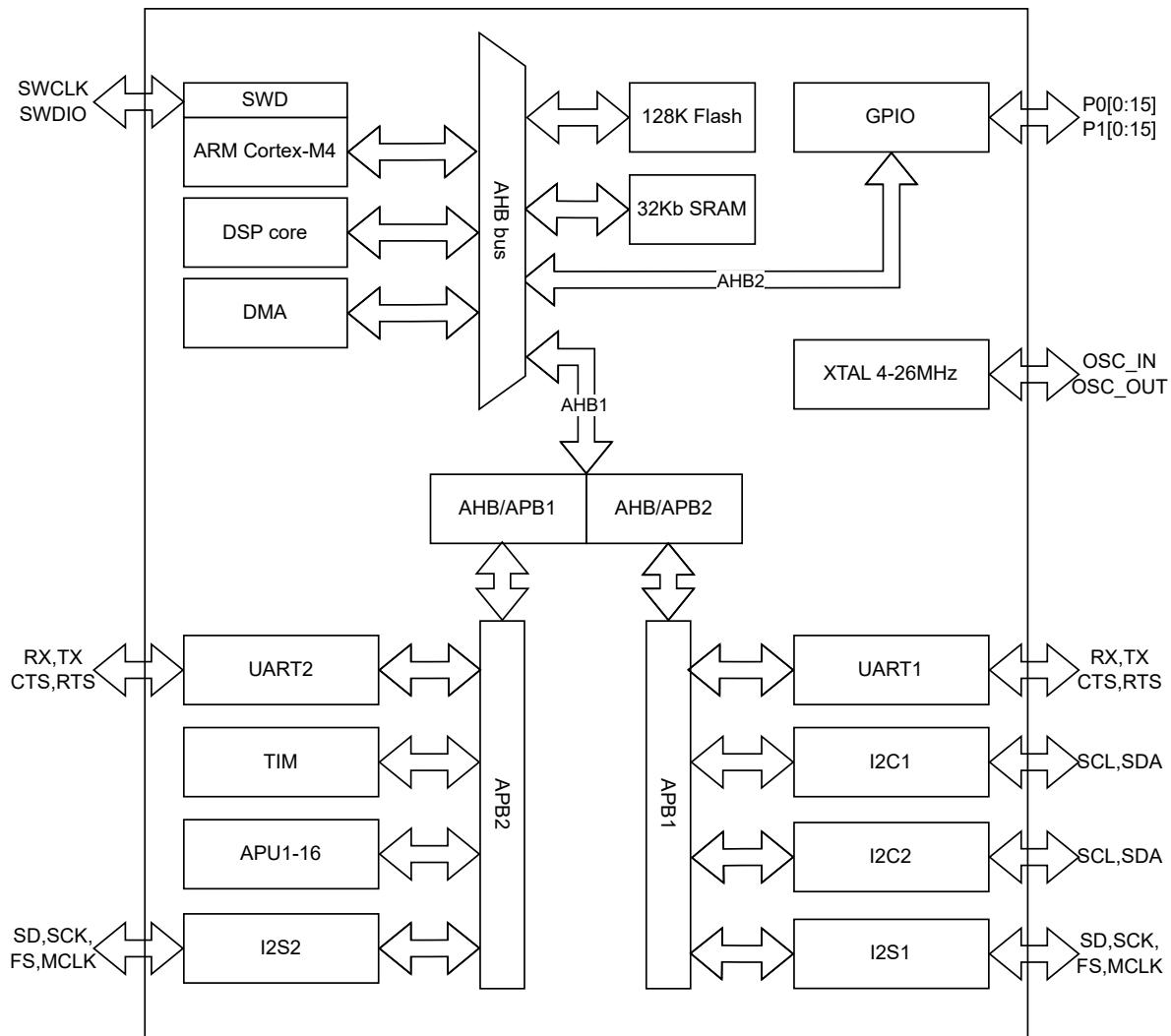

## AMT3459 Functional Diagram

Figure 1. AMT3459 block diagram

## Functional Overview

### Arm® Cortex®-M4 core with FPU

The Arm® Cortex®-M4 with FPU processor is the latest generation of Arm® processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

### Embedded Flash memory

AMT3459 devices feature 128 Kbyte of embedded Flash memory available for storing programs and data in single bank architecture. The Flash memory contains 64 pages of 2 Kbyte.

### Embedded SRAM

AMT3459 devices feature 32 Kbyte of embedded SRAM.

### Power supply management

VDD = 1.7 to 3.6 V: external power supply for I/Os (VDDIO1), the internal regulator and the system analog such as reset, power management and internal clocks. It is provided externally through VDD pins.

### Direct memory access controller (DMA)

The device embeds 1 DMA.

Direct memory access (DMA) is used in order to provide high-speed data transfer between peripherals and memory as well as memory to memory. Data can be quickly moved by DMA without any CPU actions. This keeps CPU resources free for other operations.

The DMA controller has 7 channels in total, each dedicated to managing memory access requests from one or more peripherals. Each has an arbiter for handling the priority between DMA requests.

### General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. Fast I/O toggling can be achieved thanks to their mapping on the AHB2 bus.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

## Timer

The AMT3459 includes one advanced control timer. Timer counter resolution is 16 bit.

## Inter-integrated circuit interface (I2C)

The device embeds two I2C. (I2C1, I2C2)

The I2C bus interface handles communications between the microcontroller and the serial I2C bus. It controls all I2C bus-specific sequencing, protocol, arbitration and timing.

The I2C peripheral supports:

- I2C-bus specification and user manual rev. 5 compatibility:

- Slave and master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- Fast-mode Plus (Fm+), with a bitrate up to 1 Mbit/s and 20 mA output drive I/Os

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- 1-byte buffer with DMA capability

## Universal asynchronous receiver transmitter (UART)

The AMT3459 devices have two embedded universal asynchronous receiver transmitter (UART1, UART2).

This interface provides asynchronous communication, multiprocessor communication mode, single-wire half-duplex communication mode. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

UART has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baud rates up to 204 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

The UART interface can be served by the DMA controller.

## Inter-Integrated Circuit Sound (I2S)

The device embeds two I2S (I2S1, I2S2). The I2S bus interface handles communications between the microcontroller and the serial audio protocol.

The I2S peripheral supports:

- Two independent audio sub-blocks which can be transmitters or receivers with their respective FIFO.

- 8-word integrated FIFOs for each audio sub-block.

- Synchronous or asynchronous mode between the audio sub-blocks.

- Master or slave configuration independent for both audio sub-blocks.

- Clock generator for each audio block to target independent audio frequency sampling when both audio sub-blocks are configured in master mode.

- Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit.

- Peripheral with large configurability and flexibility allowing to target as example the following audio protocol: I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF out.

- Up to 16 slots available with configurable size and with the possibility to select which ones are active in the audio frame.

- Number of bits by frame may be configurable.

- Frame synchronization active level configurable (offset, bit length, level).

- First active bit position in the slot is configurable.

- LSB first or MSB first for data transfer.

- Mute mode.

- Stereo/Mono audio frame capability.

- Communication clock strobing edge configurable (SCK).

- Error flags with associated interrupts if enabled respectively.

- Overrun and underrun detection.

- Anticipated frame synchronization signal detection in slave mode.

- Late frame synchronization signal detection in slave mode.

- Codec not ready for the AC'97 mode in reception.

- Interruption sources when enabled:

- Errors.

- FIFO requests.

- DMA interface with 2 dedicated channels to handle access to the dedicated integrated

- FIFO of each I2S audio sub-block.

## Audio Processing Unit

The device embeds 32 independent APUs.

Each APUs can be used as a programmable audio filter. Processing includes a fourth order digital IIR filter with programmable coefficients (one set per channel). This filter is implemented as cascade of two biquad sections with frequency response given by:

$$\left( \frac{N0 + 2 \times N1 \times z^{-1} + N2 \times z^{-2}}{32768 - 2 \times D1 \times z^{-1} - D2 \times z^{-2}} \right) \left( \frac{N3 + 2 \times N4 \times z^{-1} + N5 \times z^{-2}}{32768 - 2 \times D4 \times z^{-1} - D5 \times z^{-2}} \right)$$

The N and D coefficients are fully programmable, and the entire filter can be enabled.

The APU supports:

- Biquad Notch

- Biquad High Shelf

- Biquad Low Shelf

- Biquad HighPass

- Biquad LowPass

- Biquad AllPass

- Biquad BandPass Peak

- Biquad BandPass Skirt

- Biquad Peak

## Specifications

### Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)

|                                | MIN  | MAX | UNIT |

|--------------------------------|------|-----|------|

| Input voltage VDD to VSS       | -0.3 | 4   | V    |

| Operation Temperature          | -40  | 125 | °C   |

| Junction Temperature, $T_J$    | 150  | 150 | °C   |

| Storage Temperature, $T_{STG}$ | -65  | 150 | °C   |

### ESD Ratings

|                                           | VALUE                                                                | UNIT  |

|-------------------------------------------|----------------------------------------------------------------------|-------|

| Electrostatic<br>discharge<br>$V_{(ESD)}$ | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001                   | ±1900 |

|                                           | Charged-device model (CDM), per JEDEC specification JESD22-<br>VC101 | ±1500 |

### Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                                               | MIN | NOM | MAX | UNIT |

|---------------------------------------------------------------|-----|-----|-----|------|

| Voltage supply                                                | 1.7 | 3.3 | 3.6 | V    |

| Power dissipation at $TA = 105$ °C                            |     |     | 606 | mW   |

| Total current into sum of all VDD power lines                 |     |     | 160 | mA   |

| Total output current sunk by sum of all I/Os and control pins |     |     | 120 | mA   |

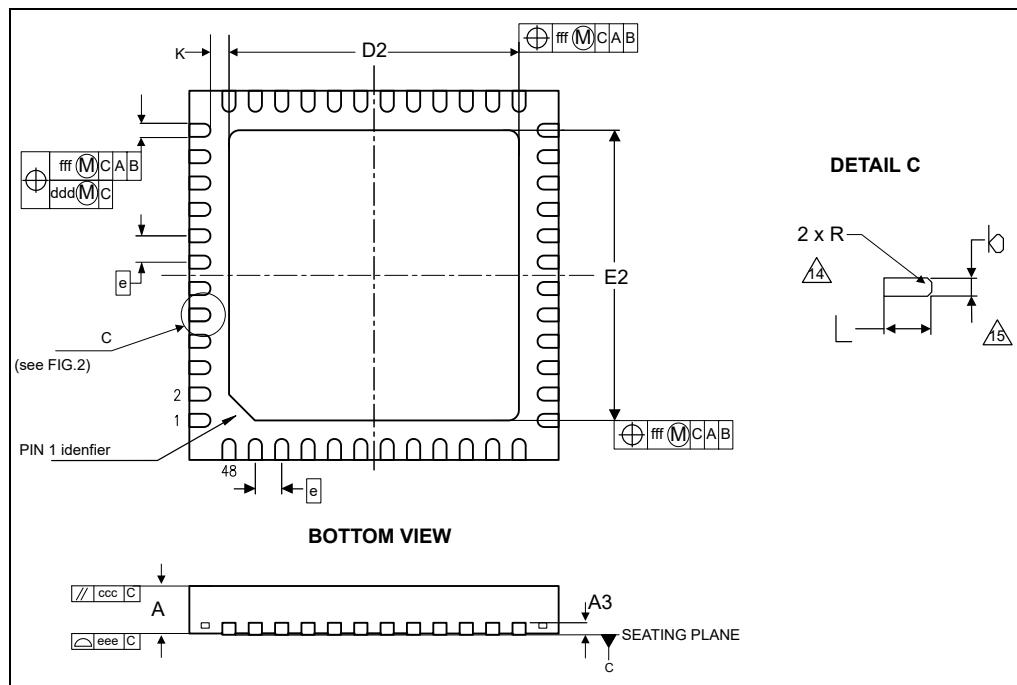

## Package information

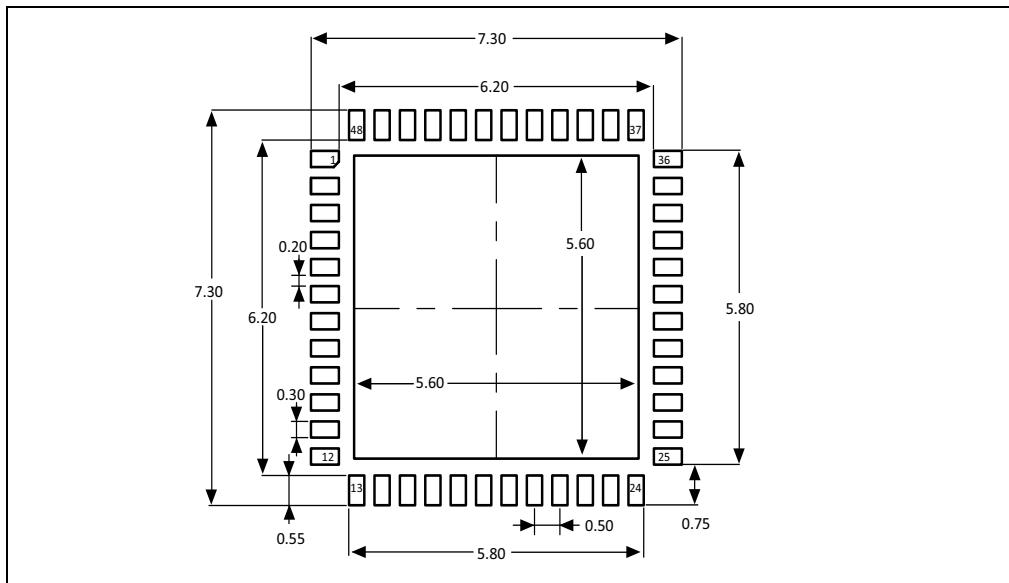

### UFQFPN48 package information

Figure 2. UFQFPN48 - 48-pin, 7x7 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline

Table 1. UFQFPN48 - 48-pin, 7x7 mm, 0.5 mm pitch ultra thin fine pitch quad flat package mechanical data

| Symbol | millimeters |       |       | inches |        |        |

|--------|-------------|-------|-------|--------|--------|--------|

|        | Min         | Typ   | Max   | Min    | Typ    | Max    |

| A      | 0.500       | 0.550 | 0.600 | 0.0197 | 0.0217 | 0.0236 |

| A1     | -           | -     | 0.050 | -      | -      | 0.0020 |

| A3     | -           | 0.152 | -     | -      | 0.0060 | -      |

| b      | 0.180       | 0.250 | 0.300 | 0.0071 | 0.0098 | 0.0118 |

| D      | 7.000       |       |       | 0.2756 |        |        |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165 | 0.2205 | 0.2244 |

| E      | 7.000       |       |       | 0.2756 |        |        |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165 | 0.2205 | 0.2244 |

| e      | -           | 0.500 | -     | -      | 0.0197 | -      |

| L      | 0.300       | -     | 0.500 | 0.0118 | -      | 0.0197 |

| ddd    | -           | 0.050 | -     | -      | 0.0020 | -      |

Figure 3. UFQFPN48 - 48-pin, 7x7 mm, 0.5 mm pitch ultra thin fine pitch quad flat package recommended footprint

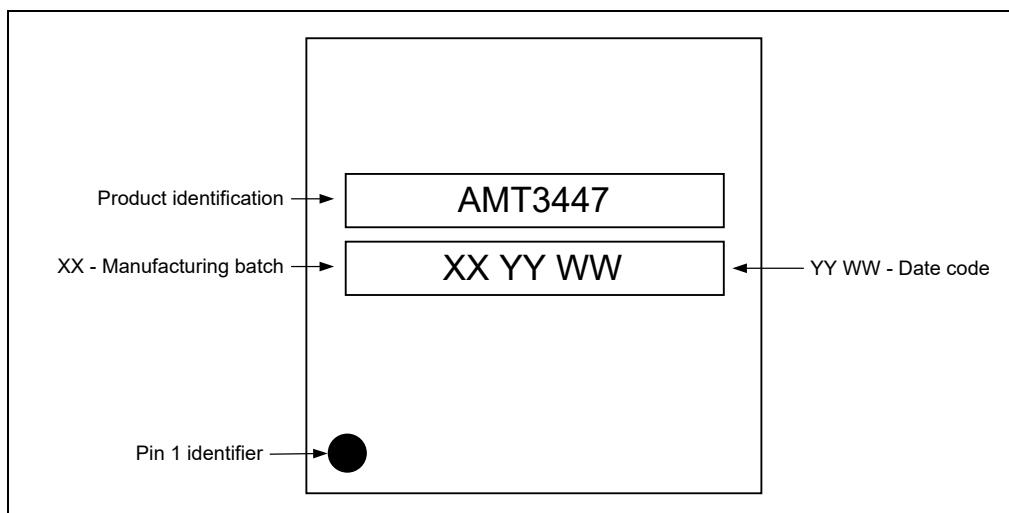

#### Device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 4. UFQFPN48 marking (package top view)